我們想讓你知道:台積電製程領先業界,除了專業分工地位明確,研發團隊全力以赴更是重要原因;未來兩年公司訂單滿載,作者認為是年輕人參與世界級任務的難得機會,不可錯過了。

上週和大家談,台積電是否讓台清交一流人才做二流工作?引發廣大迴響,點閱率破30萬,有網友問我能不能再進一步談談台積電和英特爾、三星的競爭力?為什麼台積電能,英特爾、三星卻不能?讓我們從台積電領先全球的「先進製程」與「先進封裝」二項技術談起,看看台積電領先英特爾、三星的秘密,今天先來談談先進製程。(延伸閱讀:台積電用一流人才做二流工作?專家:多虧這些高手,才能超越英特爾!)

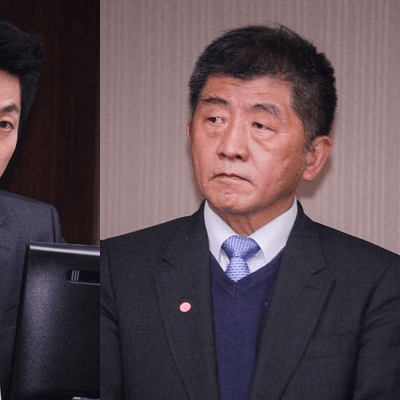

什麼是微米(μm)與奈米(nm)?

我們最常使用的長度單位是「米(m)」,也就是「公尺」,因此:

毫(mini):代表千分之一,「毫米(mm)」代表千分之一米。

微(micro):代表百萬分之一,「微米(μm)」代表百萬分之一米。

奈(nano):代表十億分之一,「奈米(nm)」代表十億分之一米。

因為微小的尺寸看不到,可能大家沒有感覺,我們來舉一些實例,如圖一所示,人類頭髮的粗細大約100微米(μm),細菌的尺寸大約1微米(μm),病毒的尺寸大約100奈米(nm),台積電的製程目前可做到10奈米(nm)以下,大約只有病毒1/10,厲害吧!未來甚至會開發小於1奈米的製程,稱為「次奈米製程」或「埃米製程」,差不多是一顆原子的大小。

什麼是積體電路(IC:Integrated Circuit)?

將電的主動元件(二極體、電晶體)與被動元件(電阻、電容、電感)縮小以後,製作在矽晶圓或砷化鎵晶圓上,稱為「積體電路(IC:Integrated Circuit)」,其中「堆積(Integrated)」與「電路(Circuit)」是指將許多電子元件堆積起來的意思。

將電子產品打開以後可以看到印刷電路板(PCB:Printed Circuit Board)如圖一所示,上面有許多長得很像「蜈蚣」的積體電路(IC),積體電路的尺寸有大有小,我們以處理器為例邊長大約20毫米(mm),上面一小塊正方形稱為「晶片(Chip)」或「晶粒(Die)」,晶片邊長大約10毫米(mm),晶片上面密密麻麻的元件稱為「電晶體(Transistor)」,電晶體邊長大約100奈米(nm),而電晶體上面尺寸最小的結構稱為「閘極長度(Gate length)」大約10奈米(nm),這個就是我們常聽到的台積電「10奈米製程」。(延伸閱讀:台積電小心,最悍對手來了!三星猛砸3.5兆,急起直追搶5奈米訂單) (相關報導: 半導體科技戰開打 夾在美中之間的台灣怎麼做? | 更多文章 )

什麼是場效電晶體(FET:Field Effect Transistor)?

電晶體的種類很多,先從大家耳熟能詳的「MOS」來說明。MOS的全名是「金屬—氧化物—半導體場效電晶體(MOSFET:Metal Oxide Semiconductor Field Effect Transistor)」, 構造如圖二所示,左邊灰色的區域叫做「源極(Source)」,右邊灰色的區域叫做「汲極(Drain)」,中間有塊金屬(紅色)突出來叫做「閘極(Gate)」,閘極下方有一層厚度很薄的氧化物(黄色),因為中間由上而下依序為金屬(Metal)、氧化物(Oxide)、半導體(Semiconductor),因此稱為「MOS」。